Bouffalo ISP Protocol V1: Difference between revisions

No edit summary |

|||

| Line 69: | Line 69: | ||

Every chip using ISP Protocol V1 have ability to get into ISP mode by specifying voltage level on specific pin during boot time. This mechanism is implemented within BootROM code. | Every chip using ISP Protocol V1 have ability to get into ISP mode by specifying voltage level on specific pin during boot time. This mechanism is implemented within BootROM code. | ||

BL602 as example, the boot pin needs to be pulled to it's according level (most of times HIGH) 0.1s before powering up the chip via PU_CHIP, and then boot pin needs to be kept at specified level at least 2ms after PU_CHIP get HIGH. | BL602 as example, the boot pin needs to be pulled to it's according level (most of times HIGH) 0.1s before powering up the chip via PU_CHIP, and then boot pin needs to be kept at specified level at least 2ms after PU_CHIP get HIGH. | ||

Revision as of 20:08, 19 May 2023

This page describes Bouffalo ISP Protocol V1, which is ISP protocol used to run images, write images to Flash or program fuses via UART, USB, SDIO or JTAG.

It is integrated in BL602, BL702, BL808 and BL616 series of chips, although, every series have some improvements to this protocol.

List of available interfaces for specific chips:

| Chip | UART | USB | SDIO | JTAG | SD Card |

|---|---|---|---|---|---|

| BL602 Series | Yes | No | Yes | ? | No |

| BL702 Series | Yes | Yes | No | ? | No |

| BL808C | Yes | Broken | ? | ? | Broken? |

| BL808D | Yes | N/A | ? | ? | N/A |

| BL606P | Yes | ? | ? | ? | N/A |

| BL616 Series | Yes | Yes | ? | ? | ? |

Getting into ISP/BootROM mode

| Currently the BootROM is not explored enough, to know how exactly the boot process works within it, although, we will describe here already known and tested boot flows. |

Currently, there are two ways of getting into ISP mode, which we will describe in next sections:

Via GPIO

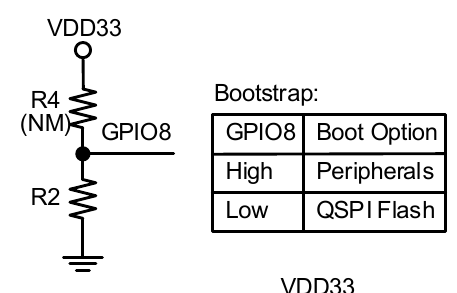

Every chip using ISP Protocol V1 have ability to get into ISP mode by specifying voltage level on specific pin during boot time. This mechanism is implemented within BootROM code.

BL602 as example, the boot pin needs to be pulled to it's according level (most of times HIGH) 0.1s before powering up the chip via PU_CHIP, and then boot pin needs to be kept at specified level at least 2ms after PU_CHIP get HIGH.

| Chip | Pin | ISP Mode when pin is | Note |

|---|---|---|---|

| BL602 Series | IO8 | High | |

| BL702 Series | IO28 | High | |

| BL808 Series | IO39 | High | Multiplexed with QSPI D3 pin |

| BL616 Series | IO2 | High |